1ST EDITION

# Accelerate Model Training with PyTorch 2.X

Build more accurate models by boosting the model training process

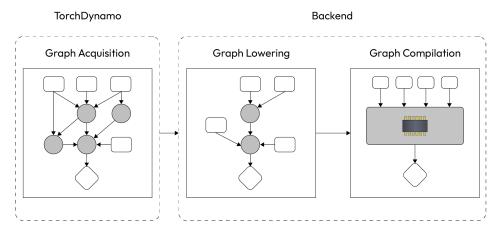

# MAICON MELO ALVES

Foreword by Prof. Lúcia Maria de Assumpção Drummond Titular professor at Fluminense Federal University, Brazil

# Accelerate Model Training with PyTorch 2.X

Build more accurate models by boosting the model training process

**Maicon Melo Alves**

# Accelerate Model Training with PyTorch 2.X

Copyright © 2024 Packt Publishing

*All rights reserved.* No part of this book may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, without the prior written permission of the publisher, except in the case of brief quotations embedded in critical articles or reviews.

Every effort has been made in the preparation of this book to ensure the accuracy of the information presented. However, the information contained in this book is sold without warranty, either express or implied. Neither the author, nor Packt Publishing or its dealers and distributors, will be held liable for any damages caused or alleged to have been caused directly or indirectly by this book.

Packt Publishing has endeavored to provide trademark information about all of the companies and products mentioned in this book by the appropriate use of capitals. However, Packt Publishing cannot guarantee the accuracy of this information.

Group Product Manager: Niranjan Naikwadi Publishing Product Manager: Sanjana Gupta Book Project Manager: Kirti Pisat Content Development Editor: Manikandan Kurup Technical Editor: Seemanjay Ameriya Copy Editor: Safis Editing Proofreader: Safis Editing and Manikandan Kurup Indexer: Hemangini Bari Production Designer: Aparna Bhagat Senior DevRel Marketing Coordinator: Vinishka Kalra

First published: April 2024

Production reference: 1050424

Published by Packt Publishing Ltd. Grosvenor House 11 St Paul's Square Birmingham B3 1RB, UK.

ISBN 978-1-80512-010-0

www.packtpub.com

To my wife and best friend, Cristiane, for being my loving partner throughout our joint life journey. To my daughters, Giovana and Camila, for being my real treasure; I'm so proud of you. To my mom, Fatima, and brothers, Johny and Karoline, for being my safe harbor. Despite everything, I also dedicate this book to my (late) father Jorge.

– Maicon Melo Alves

# Foreword

Accelerating model training is critical in the area of machine learning for several reasons. As datasets grow larger and models become more complex, training times can become prohibitively long, hindering research and development progress. This is where machine learning frameworks such as PyTorch come into play, providing tools and techniques to accelerate the training process.

PyTorch, with its flexibility, GPU acceleration, optimization techniques, and distributed training capabilities, plays a crucial role in this endeavor by enabling researchers and developers to iterate quickly, train complex models efficiently, and deploy solutions faster. By leveraging PyTorch's capabilities, practitioners can push the boundaries of what is possible in artificial intelligence and drive innovation across various domains.

Since learning all of these capabilities is not a straightforward task, this book is a great resource for all students, researchers, and professionals who intend to learn how to accelerate model training with the latest release of PyTorch in a smooth way.

This very didactic book starts by introducing how the training process works and what kind of modifications can be done at the application and environment layers to accelerate the training process.

Only after that, the following chapters describe methods to accelerate the training model, such as the Compile API, a novel capability launched in PyTorch 2.0 useful for compiling a model, and the use of specialized libraries such as OpenMP and IPEX to speed up the training process of our models even more.

It also describes the building of an efficient data pipeline to keep your GPU working at its peak for the entire training process, simplifying a model by reducing the number of parameters, and reducing the numerical precision adopted by the neural network to accelerate the training process and decrease the amount of memory needed to store the model.

Finally, this book also explains how to spread out the distributed training process to run on multiple CPUs and GPUs.

This book not only provides current and highly relevant content for the learning and updating of any professional working in the field of computing but also impresses with its extremely didactic presentation of the subject. You will certainly appreciate the quiz at the end of each chapter and the connection made between the chapters in the summary at the end of each chapter. In all chapters, codes, and examples of use are presented. For all these reasons, I believe that the book could be successfully adopted by undergraduate and graduate courses as a support bibliography for them too.

Prof. Lúcia Maria de Assumpção Drummond

Titular professor at Fluminense Federal University, Brazil

# Contributors

### About the author

**Dr. Maicon Melo Alves** is a senior system analyst and academic professor who specializes in **High-Performance Computing** (**HPC**) systems. In the last five years, he has become interested in understanding how HPC systems have been used in AI applications. To better understand this topic, he completed an MBA in data science in 2021 at Pontifícia Universidade Católica of Rio de Janeiro (PUC-RIO). He has over 25 years of experience in IT infrastructure, and since 2006, he has worked with HPC systems at Petrobras, the Brazilian state energy company. He obtained his DSc degree in computer science from the **Fluminense Federal University** (**UFF**) in 2018 and has published three books and publications in international journals in HPC.

### About the reviewer

**Dimitra Charalampopoulou** is a machine learning engineer with a background in technology consulting and a strong interest in AI and machine learning. She has led numerous large-scale digital transformation engineering projects for clients across the US and EMEA and has received various awards, including recognition for her start-up at the MIT Startup Competition. Additionally, she has been a speaker at two conferences in Europe on the topic of GenAI. As an advocate for women in tech, she is the founder and managing director of an NGO that promotes gender equality in tech and has taught programming classes to female students internationally.

# **Table of Contents**

| Preface |  |

|---------|--|

|---------|--|

### XV

19

# Part 1: Paving the Way

# 1

#### **Deconstructing the Training Process** 3 Technical requirements 3 Hyperparameters 10 Operations 11 Remembering the training process 3 Parameters 15 4 Dataset 7 The training algorithm Quiz time! 16 18 Summary Understanding the computational burden of the model training phase 9

# 2

### **Training Models Faster**

| Technical requirements                       | 19 |

|----------------------------------------------|----|

| What options do we have?                     | 20 |

| Modifying the software stack                 | 21 |

| Increasing computing resources               | 24 |

| Modifying the application layer              | 25 |

| What can we change in the application layer? | 25 |

| Getting hands-on                             | 26 |

| What if we change the batch size?            | 28 |

|----------------------------------------------|----|

| Modifying the environment layer              | 30 |

| What can we change in the environment layer? | 30 |

| Getting hands-on                             | 31 |

| Quiz time!                                   | 32 |

| Summary                                      | 34 |

|                                              |    |

# Part 2: Going Faster

# 3

### **Compiling the Model**

| Technical requirements                           | 37 | How does the Compile API work     |

|--------------------------------------------------|----|-----------------------------------|

| What do you mean by compiling?                   | 37 | under the hood?                   |

| Execution modes                                  | 38 | Compiling workflow and components |

| Model compiling                                  | 40 | Backends                          |

| Using the Compile API                            | 41 | Quiz time!                        |

| Basic usage                                      | 41 | Summary                           |

| Give me a real fight – training a heavier model! | 44 |                                   |

# 4

### **Using Specialized Libraries**

| Technical requirements             | 55 | Optimizing Intel CPU with IPEX     |

|------------------------------------|----|------------------------------------|

| Multithreading with OpenMP         | 56 | Using IPEX                         |

| What is multithreading?            | 56 | How does IPEX work under the hood? |

| Using and configuring OpenMP       | 59 | Quiz time!                         |

| Using and configuring Intel OpenMP | 63 | Summary                            |

# 5

### **Building an Efficient Data Pipeline**

| Technical requirements           | 73 | Accelerating data loading             | 78 |

|----------------------------------|----|---------------------------------------|----|

| Why do we need an efficient data |    | Optimizing a data transfer to the GPU | 78 |

| pipeline?                        | 74 | Configuring data pipeline workers     | 80 |

| What is a data pipeline?         | 74 | Reaping the rewards                   | 81 |

| How to build a data pipeline     | 75 | Quiz time!                            | 83 |

| Data pipeline bottleneck         | 77 | Summary                               | 85 |

| under the hood?                   | 48 |

|-----------------------------------|----|

| Compiling workflow and components | 48 |

| Backends                          | 50 |

| Quiz time!                        | 51 |

| Summary                           | 53 |

|                                   |    |

|                                   |    |

|                                   |    |

73

55

65 66

# Simplifying the Model

| Technical requirements                |    |

|---------------------------------------|----|

| Knowing the model                     |    |

| simplifying process                   | 88 |

| Why simplify a model? (reason)        | 88 |

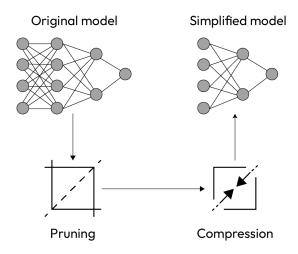

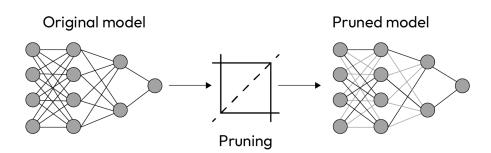

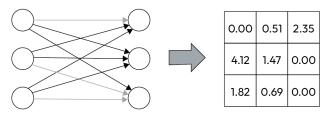

| How to simplify a model? (process)    | 90 |

| When do we simplify a model? (moment) | 94 |

|                                       |    |

|                                 | 87  |

|---------------------------------|-----|

| Using Microsoft NNI to simplify |     |

| a model                         | 94  |

| Overview of NNI                 | 94  |

| NNI in action!                  | 96  |

| Quiz time!                      | 99  |

| Summary                         | 101 |

| •                               |     |

# 7

| Adopting Mixed Precision            |     |                                       | 103 |

|-------------------------------------|-----|---------------------------------------|-----|

| Technical requirements              | 103 | Why use mixed precision?              | 110 |

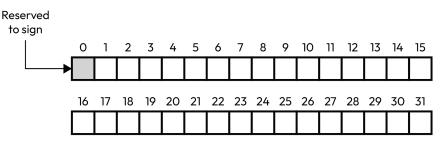

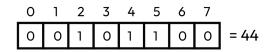

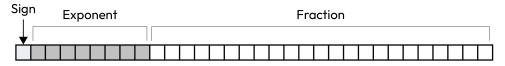

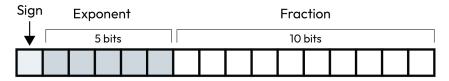

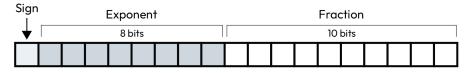

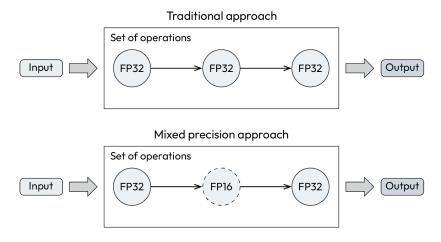

| Remembering numeric precision       | 104 | How to use mixed precision            | 112 |

| How do computers represent numbers? | 104 | How about Tensor Cores?               | 113 |

| Floating-point representation       | 105 | Enabling AMP                          | 114 |

| Novel data types                    | 106 | Activating AMP on GPU                 | 114 |

| A summary, please!                  | 108 | AMP, show us what you are capable of! | 117 |

| Understanding the mixed             |     | Quiz time!                            | 118 |

| precision strategy                  | 108 | Summary                               | 120 |

| What is mixed precision?            | 109 | Summer y                              | 120 |

# Part 3: Going Distributed

| Distributed Training at a Glance                               |            |                                                     | 123 |

|----------------------------------------------------------------|------------|-----------------------------------------------------|-----|

| Technical requirements<br>A first look at distributed training | 123<br>124 | Learning the fundamentals of parallelism strategies | 127 |

| When do we need to distribute the                              |            | Model parallelism                                   | 128 |

| training process?                                              | 124        | Data parallelism                                    | 132 |

| Where do we execute distributed training?                      | 126        |                                                     |     |

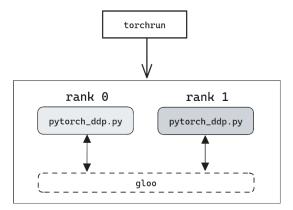

| Distributed training on PyTorch   | 135 | Quiz time! | 141 |

|-----------------------------------|-----|------------|-----|

| Basic workflow                    | 135 | Summary    | 143 |

| Communication backend and program |     |            |     |

| launcher                          | 139 |            |     |

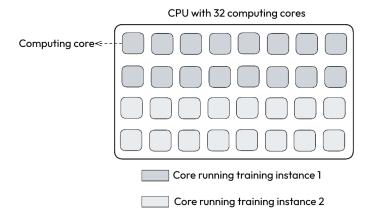

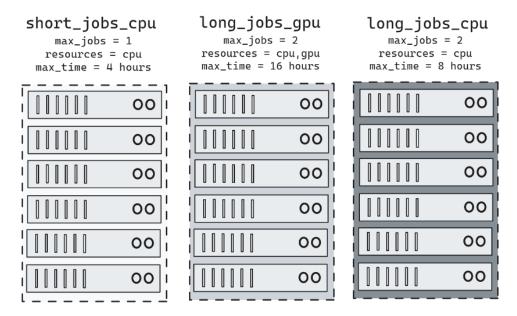

### **Training with Multiple CPUs**

| Technical requirements                  | 145 |

|-----------------------------------------|-----|

| Why distribute the training on          |     |

| multiple CPUs?                          | 146 |

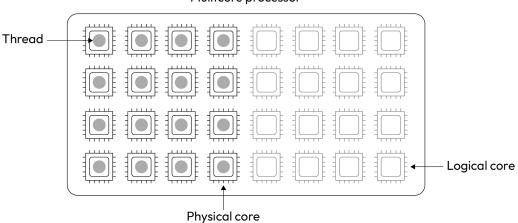

| Why not increase the number of threads? | 146 |

| Distributed training on rescue          | 147 |

| Implementing distributed training       |     |

| on multiple CPUs                        | 148 |

| The Gloo communication backend          | 148 |

|                                         |     |

#### Coding distributed training to run on multiple CPUs 149 Launching distributed training on multiple **CPUs** 152 Getting faster with Intel oneCCL 154 What is Intel oneCCL? 155 Code implementation and launching 155 Is oneCCL really better? 156 Quiz time! 157

Summary

# 10

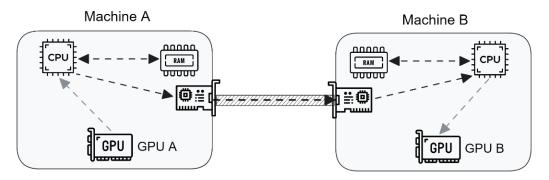

### **Training with Multiple GPUs**

| Technical requirements                   | 161 | Implementing distributed training         |

|------------------------------------------|-----|-------------------------------------------|

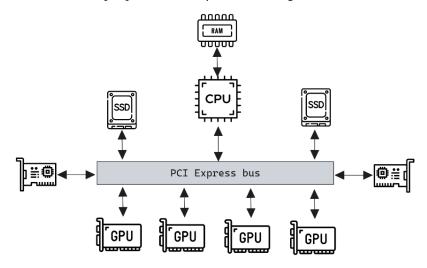

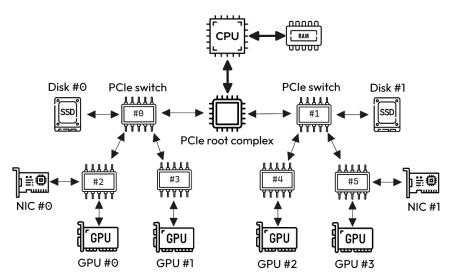

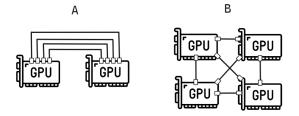

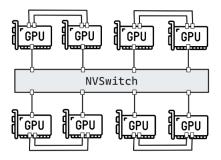

| Demystifying the multi-GPU               |     | on multiple GPUs                          |

| environment                              | 161 | The NCCL communication backend            |

| The popularity of multi-GPU environments | 162 | Coding and launching distributed training |

| Understanding multi-GPU interconnection  | 163 | with multiple GPUs                        |

| How does interconnection topology affect |     | Experimental evaluation                   |

| performance?                             | 167 | Quiz time!                                |

| Discovering the interconnection topology | 168 | Summary                                   |

| Setting GPU affinity                     | 170 | Summer y                                  |

### 161

171

171

171

173

175

177

159

| Training with Multiple Mach                               | ines     |                                      | 179 |

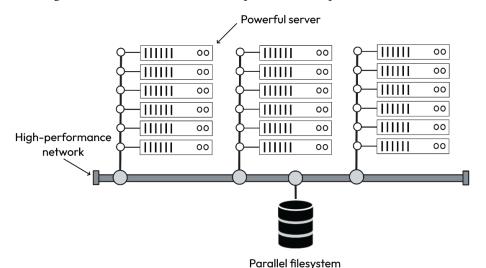

|-----------------------------------------------------------|----------|--------------------------------------|-----|

| Technical requirements                                    | 179      | Getting introduced to Open MPI       | 187 |

| What is a computing cluster?                              | 180      | Why use Open MPI and NCCL?           | 189 |

| Workload manager                                          | 181      | Coding and launching the distributed |     |

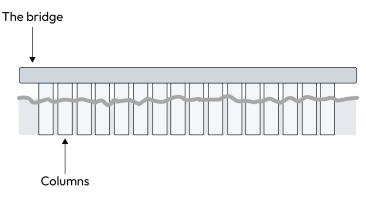

| Understanding the high-performance network                |          | training on multiple machines        | 190 |

|                                                           |          | Experimental evaluation              | 194 |

| Implementing distributed training<br>on multiple machines | g<br>187 | Quiz time!                           | 194 |

|                                                           |          | Summary                              | 197 |

| Index                                                     |          |                                      | 199 |

| Other Books You May Enjoy                                 |          |                                      | 206 |

# Preface

Hello there! I'm a system analyst and academic professor specializing in **High-Performance Computing** (**HPC**). Yes, you read it right! I'm not a data scientist. So, you are probably wondering why on Earth I decided to write a book about machine learning. Don't worry; I will explain.

HPC systems comprise powerful computing resources tightly integrated to solve complex problems. The main goal of HPC is to employ resources, techniques, and methods to accelerate the execution of highly intensive computing tasks. Traditionally, HPC environments have been used to execute scientific applications from biology, physics, chemistry, and many other areas.

But this has changed in the past few years. Nowadays, HPC systems run tasks beyond scientific applications. In fact, the most prominent non-scientific workload executed in HPC environments is precisely the subject of this book: the building process of complex neural network models.

As a data scientist, you know better than anyone else how long it could take to train complex models and how many times you need to retrain the model to evaluate different scenarios. For this reason, the usage of HPC systems to accelerate **Artificial Intelligence** (**AI**) applications (not only for training but also for inference) is a growth-demanding area.

This close relationship between AI and HPC sparked my interest in diving into the fields of machine learning and AI. By doing this, I could better understand how HPC has been applied to accelerate these applications.

So, here we are. I wrote this book to share what I have learned about this topic. My mission here is to give you the necessary knowledge to train your model faster by employing optimization techniques and methods using single or multiple computing resources.

By accelerating the training process, you can concentrate on what really matters: building stunning models!

# Who this book is for

This book is for intermediate-level data scientists, engineers, and developers who want to know how to use PyTorch to accelerate the training process of their machine learning models. Although they are not the primary audience for this material, system analysts responsible for administrating and providing infrastructure for AI workloads will also find valuable information in this book.

Basic knowledge of machine learning, PyTorch, and Python is required to get the most out of this material. However, there is no obligation to have a prior understanding of distributed computing, accelerators, or multicore processors.

### What this book covers

*Chapter 1, Deconstructing the Training Process*, provides an overview of how the training process works under the hood, describing the training algorithm and covering the phases executed by this process. This chapter also explains how factors such as hyperparameters, operations, and neural network parameters impact the training process's computational burden.

*Chapter 2, Training Models Faster*, provides an overview of the possible approaches to accelerate the training process. This chapter discusses how to modify the application and environment layers of the software stack to reduce the training time. Moreover, it explains vertical and horizontal scalability as another option to improve performance by increasing the number of resources.

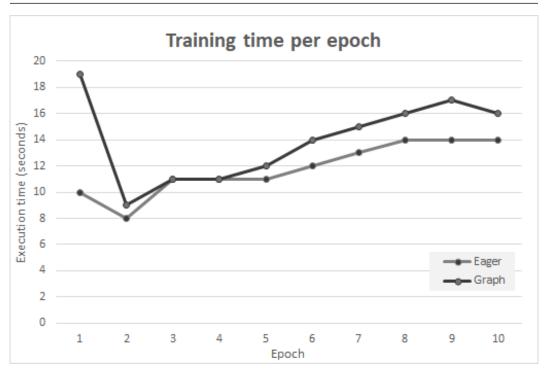

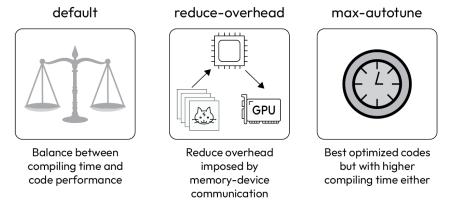

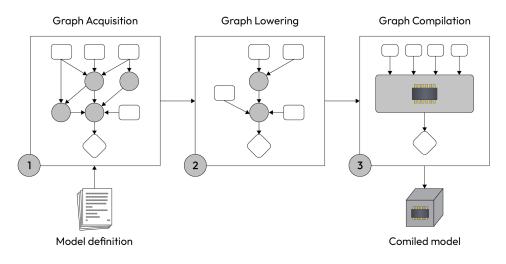

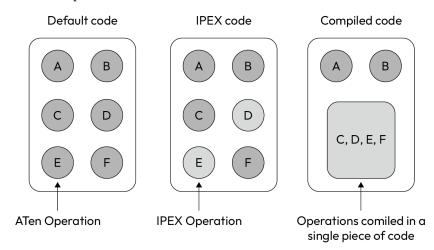

*Chapter 3, Compiling the Model*, provides an overview of the novel Compile API introduced on PyTorch 2.0. This chapter covers the differences between eager and graph modes and describes how to use the Compile API to accelerate the model-building process. This chapter also explains the compiling workflow and components involved in the compiling process.

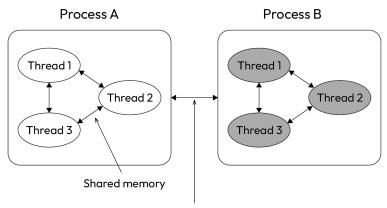

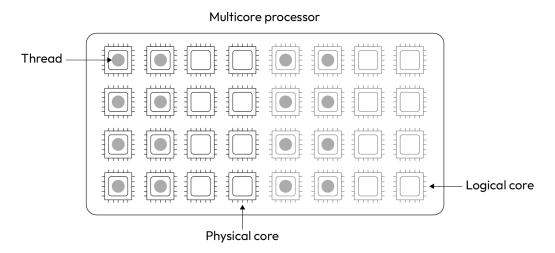

*Chapter 4*, *Using Specialized Libraries*, provides an overview of the libraries used by PyTorch to execute specialized tasks. This chapter describes how to install and configure OpenMP to deal with multithreading and IPEX to optimize the training process on an Intel CPU.

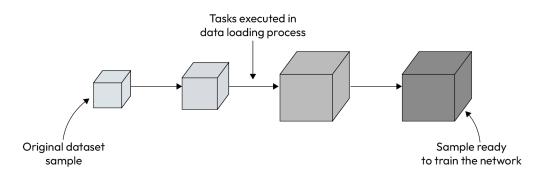

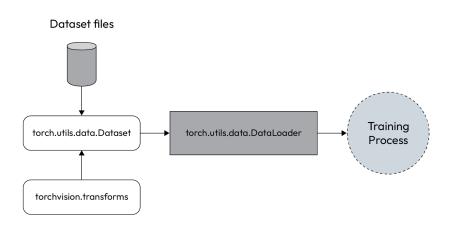

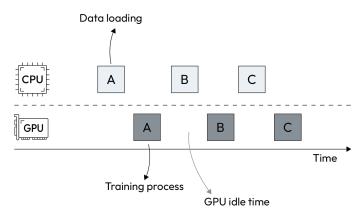

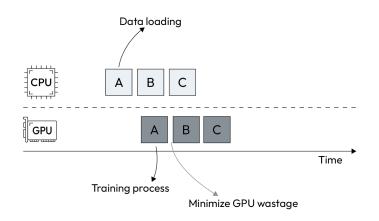

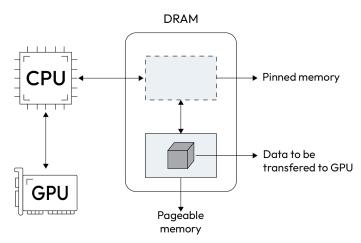

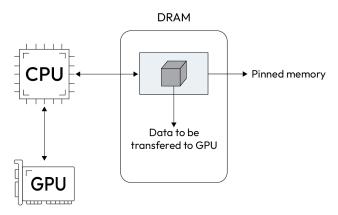

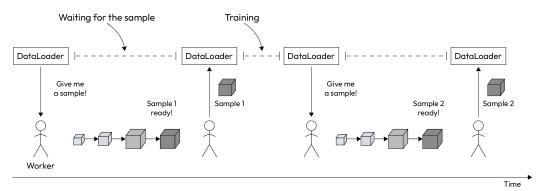

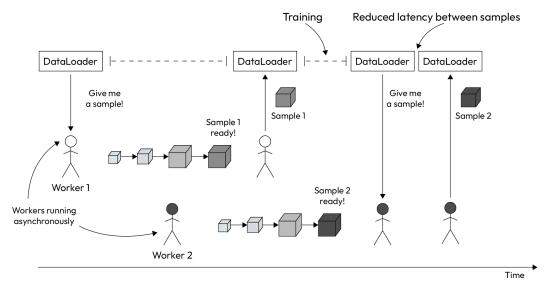

*Chapter 5*, *Building an Efficient Data Pipeline*, provides an overview of how to build an efficient data pipeline to keep the GPU working as much as possible. Besides explaining the steps executed on the data pipeline, this chapter describes how to accelerate the data-loading process by optimizing GPU data transfer and increasing the number of workers on the data pipeline.

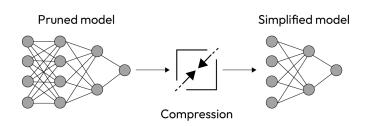

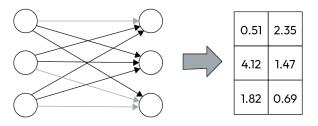

*Chapter 6*, *Simplifying the Model*, provides an overview of how to simplify a model by reducing the number of parameters of the neural network without sacrificing the model's quality. This chapter describes techniques used to reduce the model complexity, such as model pruning and compression, and explains how to use the Microsoft NNI toolkit to simplify a model easily.

*Chapter 7, Adopting Mixed Precision*, provides an overview of how to adopt a mixed precision strategy to burst the model training process without penalizing the model's accuracy. This chapter briefly explains numeric representation in computer systems and describes how to employ PyTorch's automatic mixed precision approach.

*Chapter 8, Distributed Training at a Glance,* provides an overview of the basic concepts of distributed training. This chapter presents the most adopted parallel strategies and describes the basic workflow to implement distributed training on PyTorch.

*Chapter 9, Training with Multiple CPUs*, provides an overview of how to code and execute distributed training in multiple CPUs on a single machine using a general approach and Intel oneCCL to optimize the execution on Intel platforms.

*Chapter 10, Training with Multiple GPUs*, provides an overview of how to code and execute distributed training in a multi-GPU environment on a single machine. This chapter presents the main characteristics of a multi-GPU environment and explains how to code and launch distributed training on multiple GPUs using NCCL, the default communication backend for NVIDIA GPUs.

*Chapter 11, Training with Multiple Machines*, provides an overview of how to code and execute distributed training in multiple GPUs on multiple machines. Besides an introductory explanation of computing clusters, this chapter shows how to code and launch distributed training among multiple machines using Open MPI as the launcher and NCCL as the communication backend.

### To get the most out of this book

You will need to have an understanding of the basics of machine learning, PyTorch, and Python.

| Software/hardware covered in the book | Operating system requirements |

|---------------------------------------|-------------------------------|

| PyTorch 2.X                           | Windows, Linux, or macOS      |

If you are using the digital version of this book, we advise you to type the code yourself or access the code from the book's GitHub repository (a link is available in the next section). Doing so will help you avoid any potential errors related to the copying and pasting of code.

# Download the example code files

You can download the example code files for this book from GitHub at https://github.com/ PacktPublishing/Accelerate-Model-Training-with-PyTorch-2.X. If there's an update to the code, it will be updated in the GitHub repository.

We also have other code bundles from our rich catalog of books and videos available at https://github.com/PacktPublishing/.Check them out!

# **Conventions used**

There are a number of text conventions used throughout this book.

Code in text: Indicates code words in text, database table names, folder names, filenames, file extensions, pathnames, dummy URLs, user input, and Twitter handles. Here is an example: "The ipex.optimize function returns an optimized version of the model."

A block of code is set as follows:

```

config_list = [{

'op_types': ['Linear'],

'exclude_op_names': ['layer4'],

'sparse_ratio': 0.3

}]

```

When we wish to draw your attention to a particular part of a code block, the relevant lines or items are set in bold:

```

def forward(self, x):

out = self.layer1(x)

out = self.layer2(out)

out = out.reshape(out.size(0), -1)

out = self.fcl(out)

out = self.fc2(out)

return out

```

Any command-line input or output is written as follows:

```

maicon@packt:~$ nvidia-smi topo -p -i 0,1

Device 0 is connected to device 1 by way of multiple PCIe

```

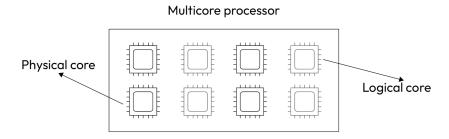

**Bold**: Indicates a new term, an important word, or words that you see onscreen. For instance, words in menus or dialog boxes appear in **bold**. Here is an example: "**OpenMP** is a library used for parallelizing tasks by harnessing all the power of multicore processors by using the multithreading technique."

Tips or important notes Appear like this.

### Get in touch

Feedback from our readers is always welcome.

**General feedback**: If you have questions about any aspect of this book, email us at customercare@ packtpub.com and mention the book title in the subject of your message.

**Errata**: Although we have taken every care to ensure the accuracy of our content, mistakes do happen. If you have found a mistake in this book, we would be grateful if you would report this to us. Please visit www.packtpub.com/support/errata and fill in the form.

**Piracy**: If you come across any illegal copies of our works in any form on the internet, we would be grateful if you would provide us with the location address or website name. Please contact us at copyright@packt.com with a link to the material.

If you are interested in becoming an author: If there is a topic that you have expertise in and you are interested in either writing or contributing to a book, please visit authors.packtpub.com.

### **Share Your Thoughts**

Once you've read *Accelerate Model Training with PyTorch 2.X*, we'd love to hear your thoughts! Please click here to go straight to the Amazon review page for this book and share your feedback.

Your review is important to us and the tech community and will help us make sure we're delivering excellent quality content.

### Download a free PDF copy of this book

Thanks for purchasing this book!

Do you like to read on the go but are unable to carry your print books everywhere?

Is your eBook purchase not compatible with the device of your choice?

Don't worry, now with every Packt book you get a DRM-free PDF version of that book at no cost.

Read anywhere, any place, on any device. Search, copy, and paste code from your favorite technical books directly into your application.

The perks don't stop there, you can get exclusive access to discounts, newsletters, and great free content in your inbox daily

Follow these simple steps to get the benefits:

1. Scan the QR code or visit the link below

https://packt.link/free-ebook/978-1-80512-010-0

- 2. Submit your proof of purchase

- 3. That's it! We'll send your free PDF and other benefits to your email directly

# Part 1: Paving the Way

In this part, you will learn about performance optimization, before delving into the techniques, approaches, and strategies described throughout the book. First, you will learn about the aspects of the training process that make it so computationally heavy. After that, you will learn about the possible approaches to reduce the training time.

This part has the following chapters:

- Chapter 1, Deconstructing the Training Process

- Chapter 2, Training Models Faster

# 1 Deconstructing the Training Process

We already know that training neural network models takes a long time to finish. Otherwise, we would not be here discussing ways to run this process faster. But which characteristics make the building process of these models so computationally heavy? Why does the training step take so long? To answer these questions, we need to understand the computational burden of the training phase.

In this chapter, we will first remember how the training phase works under the hood. We will understand what makes the training process so computationally heavy.

Here is what you will learn as part of this first chapter:

- Remembering the training process

- Understanding the computational burden of the training phase

- Understanding the factors that influence training time

### **Technical requirements**

You can find the complete code of the examples mentioned in this chapter in the book's GitHub repository at https://github.com/PacktPublishing/Accelerate-Model-Training-with-PyTorch-2.X/blob/main.

You can access your favorite environment to execute this notebook, such as Google Colab or Kaggle.

### Remembering the training process

Before describing the computational burden imposed by neural network training, we must remember how this process works.

#### Important note

This section gives a very brief introduction to the training process. If you are totally unfamiliar with this topic, you should invest some time to understand this theme before moving to the following chapters. An excellent resource for learning this topic is the book entitled *Machine Learning with PyTorch and Scikit-Learn*, published by Packt and written by Sebastian Raschka, Yuxi (Hayden) Liu, and Vahid Mirjalili.

Basically speaking, neural networks learn from examples, similar to a child observing an adult. The learning process relies on feeding the neural network with pairs of input and output values so that the network catches the intrinsic relation between the input and output data. Such relationships can be interpreted as the knowledge obtained by the model. So, where a human sees a bunch of data, the neural network sees veiled knowledge.

This learning process depends on the dataset used to train a model.

### Dataset

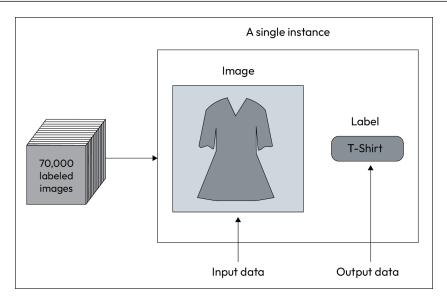

A **dataset** comprises a set of **data instances** related to some problem, scenario, event, or phenomenon. Each instance has features and target information corresponding to the input and output data. The concept of a dataset instance is similar to a registry in a table or relational database.

The dataset is usually split into two parts: training and testing sets. The training set is used to train the network, whereas the testing part is used to test the model against unseen data. Occasionally, we can also use another part to validate the model after each training iteration.

Let's look at Fashion-MNIST, a famous dataset that is commonly used to test and teach neural networks. This dataset comprises 70,000 labeled images of clothes and accessories such as dresses, shirts, and sandals belonging to 10 distinct classes or categories. The dataset is split into 60,000 instances for training and 10,000 instances for testing.

As shown in *Figure 1.1*, a single instance of this dataset comprises a 28 x 28 grayscale image and a label identifying its class. In the case of Fashion-MNIST, we have 70,000 instances, which is often referred to as the length of the dataset.

Figure 1.1 - Concept of a dataset instance

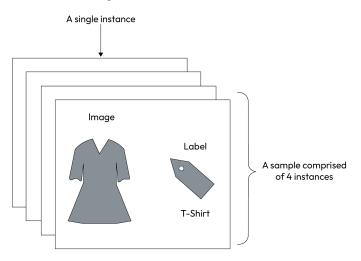

Besides the concept of dataset instance, we also have the concept of a **dataset sample**. A sample is defined as a group of instances, as shown in *Figure 1.2*. Usually, the training process executes on samples and not just on a single dataset instance. The reason why the training process takes samples instead of single instances is related to the way the training algorithm works. Don't worry about this topic; we will cover it in the following sections:

Figure 1.2 – Concept of a dataset sample

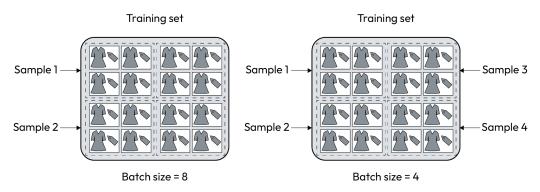

The number of instances in a sample is called the **batch size**. For example, if we divide the Fashion-MNIST training set into samples of a batch size equal to 32, we get 1,875 samples since this set has 60,000 instances.

The higher the batch size, the lower the number of samples in a training set, as pictorially described in *Figure 1.3*:

Figure 1.3 - Concept of batch size

With a batch size equal to eight, the dataset in the example is divided into two samples, each with eight dataset instances. On the other hand, with a lower batch size (in this case, four), the training set is divided into a higher number of samples (four samples).

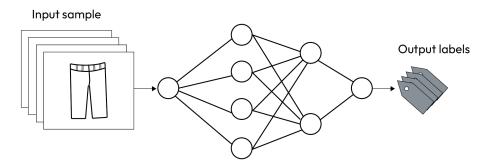

The neural network receives input samples and outputs a set of results, each corresponding to an instance of the input sample. In the case of a model to treat the classification image problem of Fashion-MNIST, the neural network gets a set of images and outputs another set of labels, as you can see in *Figure 1.4*. Each one of these labels indicates the corresponding class of the input image:

Figure 1.4 – Neural networks work on input samples

To extract the intrinsic knowledge present in the dataset, we need to submit the neural network to a training algorithm so it can learn the pattern present in the data. Let's jump to the next section to understand how this algorithm works.

### The training algorithm

The training algorithm is an **iterative process** that takes each dataset sample and adjusts the neural network parameters according to the degree of error related to the difference between the correct result and the predicted one.

A single training iteration is called the **training step**. So, the number of training steps executed in the learning process equals the number of samples used to train the model. As we stated before, the batch size defines the number of samples, which also determines the number of training steps.

After executing all the training steps, we say the training algorithm has completed a **training epoch**. The developer must define the number of epochs before starting the model-building process. Usually, the developer determines the number of epochs by varying it and evaluating the accuracy of the resultant model.

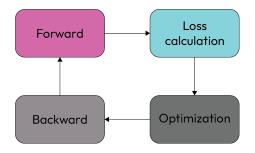

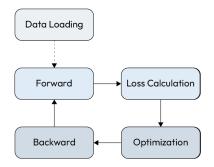

A single training step executes the four phases sequentially, as illustrated in *Figure 1.5*:

Figure 1.5 – The four phases of the training process

Let's go through each one of these steps to understand their role in the entire training process.

### Forward

In the forward phase, the neural network receives the input data, performs calculations, and outputs a result. This output is also known as the value predicted by the neural network. In the case of Fashion-MNIST, the input data is the grayscale image and the predicted value is the class to which the item belongs.

Considering the tasks executed in the training step, the forward phase has a higher computational cost. This happens because it executes all the heavy computations involved in the neural network. Such computations, commonly known as operations, will be explained in the next section.

It is interesting to note that the forward phase is exactly the same as the inference process. When using the model in practice, we continuously execute the forward phase to infer a value or result.

### Loss calculation

After the forward phase, the neural network will output a predicted value. Then, the training algorithm needs to compare the predicted value with the expected one to see how good the prediction made by the model is.

If the predicted value is close or equal to the real value, the model is performing as expected and the training process is going in the right direction. Otherwise, the training step needs to quantify the error achieved by the model to adjust the parameters proportionally to the error degree.

### Important note

In the terminology of neural networks, this error is usually referred to as **loss** or **cost**. So, it is common to see names such as loss or cost function in the literature when addressing this topic.

There are different kinds of loss functions, each one suitable to treat a specific sort of problem. The **cross-entropy** (**CE**) loss function is used in multiclass image classification problems, where we need to classify an image within a group of classes. For example, this loss function can be used in the Fashion-MNIST problem. Suppose we have just two classes or categories. In that case, we face a binary class problem, so using the **binary cross-entropy** (**BCE**) function rather than the original cross-entropy loss function is recommended.

For regression problems, the loss function is completely different from the ones used in classification problems. We can use functions such as the **mean squared error** (**MSE**), which measures the squared difference between the original value and the predicted value by the neural network.

### Optimization

After obtaining the loss, the training algorithm calculates the partial derivative of the loss function concerning the current parameters of the network. This operation results in the so-called **gradient**, which the training process uses to adjust network parameters.

Leaving the mathematical foundations aside, we can think of the gradient as the change we need to apply to network parameters to minimize the error or loss.

### Important note

You can find more information about the math used in deep learning by reading the book *Hands-On Mathematics for Deep Learning*, published by Packt and written by Jay Dawani.

Similar to the loss function, we also have distinct implementations of optimizers. The **stochastic gradient descent** (**SGD**) and Adam are used the most.

#### Backward

To finish the training process, the algorithm updates the network parameters according to the gradient obtained in the optimization phase.

#### Important note

This section provides a theoretical explanation of the training algorithm. So, be aware that depending on the machine learning framework, the training process can have a set of phases that is different from the ones in the preceding list.

Essentially, these phases constitute the computational burden of the training process. Follow me to the next section to understand how this computational burden is impacted by different factors.

# Understanding the computational burden of the model training phase

Now that we've brushed up on how the training process works, let's understand the computational cost required to train a model. By using the terms computational cost or burden, we mean the computing power needed to execute the training process. The higher the computational cost, the higher the time taken to train the model. In the same way, the higher the computational burden, the higher the computing resources required to train the model.

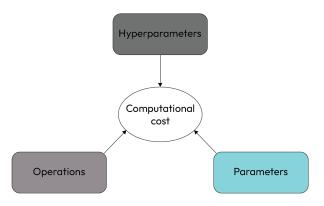

Essentially, we can say the computational burden to train a model is defined by a three-fold factor, as illustrated in *Figure 1.6*:

Figure 1.6 – Factors that influence the training computational burden

Each one of these factors contributes (to some degree) to the computational complexity imposed by the training process. Let's talk about each one of them.

### Hyperparameters

**Hyperparameters** define two aspects of neural networks: the neural network configuration and how the training algorithm works.

Concerning neural network configuration, the hyperparameters determine the number and type of layers and the number of neurons in each layer. Simple networks have a few layers and neurons, whereas complex networks have thousands of neurons spread in hundreds of layers. The number of layers and neurons determines the number of parameters of the network, which directly impacts the computational burden. Due to the significant influence of the number of parameters in the computational cost of the training step, we will discuss this topic later in this chapter as a separate performance factor.

Regarding how the training algorithm executes the training process, hyperparameters control the number of epochs and steps and determine the optimizer and loss function used during the training phase, among other things. Some of these hyperparameters have a tiny influence on the computational cost of the training process. For example, if we change the optimizer from SGD to Adam, we will not face any relevant impact on the computational cost of the training process.

Other hyperparameters can definitely raise the training phase time, though. One of the most emblematic examples is the batch size. The higher the batch size, the fewer training steps are needed to train a model. So, with a few training steps, we can speed up the building process since the training phase will execute fewer steps per epoch. On the other hand, we can spend more time executing a single training step if we have big batch sizes. This happens because the forward phase executed on each training step should deal with a higher dimensional input data. In other words, we have a trade-off here.

For example, consider the case of a batch size equal to 32 for the Fashion-MNIST dataset. In this case, the input data dimension is  $32 \times 1 \times 28 \times 28$ , where 32, 1, and 28 represent the batch size, the number of channels (colors, in this scenario), and the image size, respectively. Therefore, for this case, the input data comprises 25,088 numbers, which is the number of numbers the forward phase should compute. However, if we increase the batch size to *128*, the input data changes to 100,352 numbers, which can result in a longer time to execute a single forward phase iteration.

In addition, a bigger input sample requires a higher amount of memory to execute each training step. Depending on the hardware configuration, the amount of memory required to execute the training step can drastically reduce the performance of the entire training process or even make it impossible to execute in that hardware. Conversely, we can accelerate the training process by using hardware endowed with huge memory resources. This is why we need to know the details of the hardware resources we use and what factors influence the computational complexity of the training process.

We will dive into all of these issues throughout the book.

### Operations

We already know each training step executes four training phases: forward, loss computation, optimization, and backward. In the forward phase, the neural network receives the input data and processes it according to the neural network's architecture. Besides other things, the architecture defines the network layers, where each layer has one or more operations that the network executes during the forward phase.

For example, a **fully connected neural network** (**FCNN**) usually executes general matrix-to-matrix multiplication operations, whereas **convolutional neural networks** (**CNNs**) execute special computer vision operations such as convolution, padding, and pooling. It turns out that the computational complexity of one operation is not the same as another. So, depending on the network architecture and the operations, we can get distinct performance behavior.

Nothing is better than an example, right? Let's define a class to instantiate a traditional CNN model that is able to deal with the Fashion-MNIST dataset.

#### Important note

The complete code shown in this section is available at https://github.com/ PacktPublishing/Accelerate-Model-Training-with-PyTorch-2.X/ blob/main/code/chapter01/cnn-fashion\_mnist.ipynb.

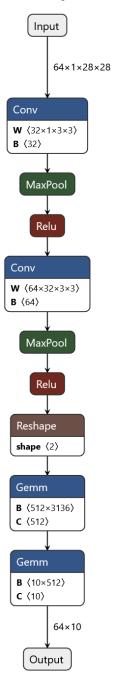

This model receives an input sample of size  $64 \times 1 \times 28 \times 28$ . This means the model receives 64 grayscale images (one channel) with a height and width equal to 28 pixels. As a result, the model outputs a tensor of dimension  $64 \times 10$ , which represents the probability of the image belonging to each of the 10 categories of the Fashion-MNIST dataset.

The model has two convolutional and two fully connected layers. Each convolutional layer comprises one bidimensional convolution, the **rectified linear unit** (**ReLU**) activation function, and pooling. The first fully connected layer has 3,136 neurons connected to the 512 neurons of the fully connected second layer. The second layer is then connected to the 10 neurons of the output layer.

### Important note

If you are unfamiliar with CNN models, it would be useful to watch the video *What is a convolutional neural network (CNN)*? from the Packt YouTube channel at https://youtu.be/K\_BHmztRTpA.

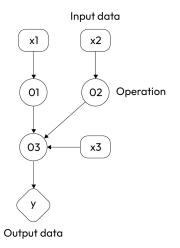

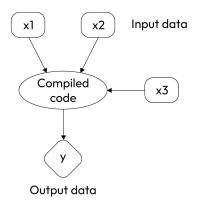

By exporting this model to the ONNX format, we get the diagram illustrated in *Figure 1.7*:

Figure 1.7 – Operations of a CNN model

#### Important note

The **Open Neural Network Exchange** (**ONNX**) is an open standard for machine learning interoperability. Besides other things, ONNX provides a standard format to export neural network models from many distinct frameworks and tools. We can use the ONNX file to inspect model details, import it into another framework, or execute the inference process.

By evaluating Figure 1.7, we can see five distinct operations:

- Conv: Bidimensional convolution

- MaxPool: Max pooling

- Relu: Activation function (ReLU)

- Reshape: Tensor dimensional transformation

- Gemm: General matrix multiplication

So, under the hood, the neural network executes these operations in the forward phase. From a computing perspective, this is the set of real operations that the machine runs during each training step. Therefore, we can rethink the training process of this model in terms of its operations and write it as a simpler algorithm:

```

for each epoch

for each training step

result = conv(input)

result = maxpool(result)

result = relu(result)

result = conv(result)

result = maxpool(result)

result = relu(result)

result = relu(result)

result = gemm(result)

result = gemm(result)

loss = calculate_loss(result)

gradient = optimization(loss)

backwards(gradient)

```

As you can see, the training process is just a set of operations executed one after another. Despite the functions or classes used to define the model, the machine is actually running this set of operations.

It turns out that each operation has a particular computational complexity, thus requiring distinct levels of computing power and resources to be executed satisfactorily. In this way, we can face different performance gains and bottlenecks for each one of those operations. Similarly, some operations can be more suitable to execute in a given hardware architecture, as we will see throughout the book.

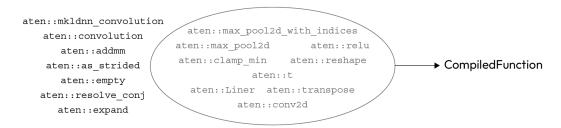

To obtain the practical meaning of this topic, we can check the percentage of time these operations spent during the training step. So, let's use **PyTorch Profiler** to get the percentage of CPU usage for each operation. The following list resumes the CPU usage when running the forward phase of our CNN model with one input sample of the Fashion-MNIST dataset:

```

aten::mkldnn_convolution: 44.01%

aten::max pool2d with indices: 30.01%

aten::addmm: 13.68%

aten::clamp min: 6.96%

aten::convolution: 1.18%

aten::copy : 0.70%

aten::relu: 0.59%

aten::_convolution: 0.49%

aten::empty: 0.35%

aten:: reshape alias: 0.31%

aten::t: 0.31%

aten::conv2d: 0.24%

aten::as strided : 0.24%

aten::reshape: 0.21%

aten::linear: 0.21%

aten::max pool2d: 0.17%

aten::expand: 0.14%

aten::transpose: 0.10%

aten::as strided: 0.07%

aten::resolve conj: 0.00%

```

#### Important note

ATen is a C++ library used by PyTorch to execute basic operations. You can find more information about this library at https://pytorch.org/cppdocs/#aten.

The results show the Conv operation (labeled here as aten::mkldnn\_convolution) presented higher CPU usage (44%), followed by the MaxPool operation (aten:: max\_pool2d\_with\_ indices), with 30% CPU usage. On the other hand, the ReLU (aten::relu) and Reshape (aten::reshape) operations consumed less than 1% of the total CPU usage. Finally, the Gemm operation (aten::addmm) used around 14% of the CPU time.

From this simple profiling test, we can assert the operations involved in the forward phase; hence, in the training process, there are distinct levels of computational complexity. We can see the training process consumed much more CPU cycles when executing the Conv operation than the Gemm operation. Notice that our CNN model has two layers comprising both operations. Thus, in this example, both operations are executed the same number of times.

Based on this knowledge about the distinct computational burden of neural network operations, we can choose the best hardware architecture or software stack to reduce the execution time of the predominant operation of a given neural network. For example, suppose we need to train a CNN composed of dozens of convolutional layers. In that case, we will look for hardware resources endowed with special capabilities to execute Conv operations more efficiently. Even though the model has some fully connected layers, we already know that the Gemm operation can be less computationally intensive than Conv. This justifies prioritizing a hardware resource that is able to accelerate convolutional operations to train that model.

### Parameters

Besides hyperparameters and operations, the neural network parameters are another factor that has a relevant influence on the computational cost of the training process. As we discussed earlier, the number and type of layers in the neural network configuration define the total number of parameters on the network.

Obviously, the higher the number of parameters, the higher the computational burden of the training process. These parameters comprise kernel values employed on convolutional operations, biases, and the weights of connections between neurons.

Our CNN model, with just 4 layers, has 1,630,090 parameters. We can easily count the total number of parameters in PyTorch by using this function:

```

def count_parameters(model):

parameters = list(model.parameters())

total_parms = sum(

[np.prod(p.size()) for p in parameters if p.requires_grad])

return total_parms

```

If we add an extra fully connected layer with 256 neurons to our CNN model and rerun this function, we will get 1,758,858 parameters in total, representing an increase of nearly 8%.

After training and testing this new CNN model, we got the same accuracy as before. Then, paying attention to the trade-off between network complexity and model accuracy is essential. On many occasions, increasing the number of layers and neurons will not necessarily result in better efficiency but will possibly increase the time of the training process.

Another aspect of parameters is the numeric precision used to represent these numbers in the model. We will dive into this topic in *Chapter 7*, *Adopting Mixed Precision*, but for now, keep in mind that the number of bytes used to represent parameters pays a relevant contribution to the time needed to train a model. So, not only does the number of parameters have an impact on training time but so does the numeric precision chosen to represent these numbers in the model.

The next section brings a couple of questions to help you retain what you have learned in this chapter.

## Quiz time!

Let's review what we have learned in this chapter by answering eight questions. At first, try to answer these questions without consulting the material.

#### Important note

```

The answers to all these questions are available at https://github.com/

PacktPublishing/Accelerate-Model-Training-with-PyTorch-2.X/

blob/main/quiz/chapter01-answers.md.

```

Before starting the quiz, remember that it is not a test at all! This section aims to complement your learning process by revising and consolidating the content covered in this chapter.

Choose the correct option for the following questions:

- 1. Which phases comprise the training process?

- A. Forward, processing, optimization, and backward.

- B. Processing, pre-processing, and post-processing.

- C. Forward, loss calculation, optimization, and backward.

- D. Processing, loss calculation, optimization, and post-processing.

- 2. Which factors impact the computational burden of the training process?

- A. Loss function, optimizer, and parameters.

- B. Hyperparameters, parameters, and operations.

- C. Hyperparameters, loss function, and operations.

- D. Parameters, operations, and loss function.

- 3. After executing the training algorithm on all dataset samples, the training process has completed a training what?

- A. Evolution.

- B. Epoch.

- C. Step.

- D. Generation.

- 4. A dataset sample comprises a set of what?

- A. Dataset collections.

- B. Dataset steps.

- C. Dataset epochs.

- D. Dataset instances.

- 5. Which hyperparameter is more likely to increase the computational burden of the training process?

- A. Batch size.

- B. Optimizer.

- C. Number of epochs.

- D. Learning rate.

- 6. A training set has 2,500 instances. By defining a batch size equal to 1 and 50, the number of steps executed during the training process is, respectively, which of the following?

- A. 500 and 5.

- B. 2,500 and 1.

- C. 2,500 and 50.

- D. 500 and 50.

- 7. The profiling of a training process showed that the most time-consuming operation was aten::mkldnn\_convolution. In this case, what is the heavier computing phase of the training process?

- A. Backward.

- B. Forward.

- C. Loss calculation.

- D. Optimization.

- 8. A model has two convolutional layers and two fully connected layers. If we add two more convolutional layers to the model, it will increase the number of what?

- A. Hyperparameters.

- B. Training steps.

- C. Parameters.

- D. Training samples.

Let's summarize what we've learned in this chapter.

## Summary

We have reached the end of the first step of our training acceleration journey. You started this chapter by remembering how the training process works. In addition to refreshing concepts such as datasets and samples, you remembered the four phases of the training algorithm.

Next, you learned that hyperparameters, operations, and parameters are the three-fold factors influencing the training process's computational burden.

Now that you have remembered the training process and understood what contributes to its computational complexity, it's time to move on to the next topic.

Let's take our first steps to learn how to accelerate this heavy computational process!

# 2

## **Training Models Faster**

In the last chapter, we learned the factors that contribute to increasing the computational burden of the training process. Those factors have a direct influence on the complexity of the training phase and, hence, on the execution time.

Now, it is time to learn how to accelerate this process. In general, we can improve performance by changing something in the software stack or increasing the number of computing resources.

In this chapter, we will start to understand both of these options. Next, we will learn what can be modified in the application and environment layers.

Here is what you will learn as part of this chapter:

- Understanding the approaches to accelerate the training process

- Knowing the layers of the software stack used to train a model

- Learning the difference between vertical and horizontal scaling

- Understanding what can be changed in the application layer to accelerate the training process.

- Understanding what can be changed in the environment layer to improve the performance of the training phase

## **Technical requirements**

You can find the complete code of the examples mentioned in this chapter in the book's GitHub repository at https://github.com/PacktPublishing/Accelerate-Model-Training-with-PyTorch-2.X/blob/main.

You can access your favorite environments to execute this notebook, such as Google Colab or Kaggle.

## What options do we have?

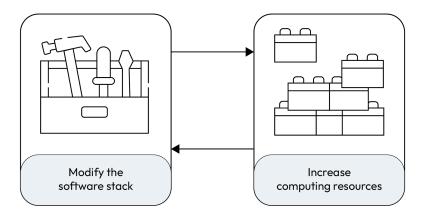

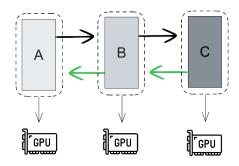

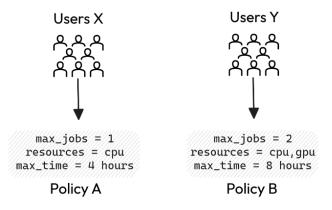

Once we have decided to accelerate the training process of a model, we can take two directions, as illustrated in *Figure 2.1*:

Figure 2.1 – Approaches to accelerating the training phase

In the first option (**Modify the software stack**), we go through each layer of the software stack used to train a model to seek opportunities to improve the training process. In simpler words, we can change the application code, install and use a specialized library, or enable a special capability regarding the operating system or container environment.

This first approach relies on having profound knowledge of performance tuning techniques. In addition, it demands a high sense of investigation to identify bottlenecks and apply the most suitable solution to overcome them. Thus, this approach is about harnessing the most hardware and software resources by extracting the maximum performance of the computing system.

Nevertheless, remark that depending on the environment we are running the training process in, we may not have the required privileges to change the lower layers of the software stack. For example, suppose we are running the training process in a notebook provided by a third-party environment such as **Kaggle** or **Google Colab**. In this case, we cannot change operating system parameters or modify the container image because this environment is controlled and restricted. We can still change the application code, but it may not be enough to accelerate the training process.

When changing things in the software stack is impossible or does not provide the expected performance gain, we can go towards the second option (**Increase computing resources**) to train the model. So, we can increase the number of processors and the amount of main memory, use accelerator devices, or spread the training process across multiple machines. Naturally, we may need to spend money to bring this option to life.

Notice that this approach is easier in the cloud than for on-premises infrastructures. When using the cloud, we can easily contract a machine endowed with accelerator devices or add more machines to our setup. We can get these resources ready to use with a few clicks. On the other hand, we may face some constraints when adding new computing resources to the on-premises infrastructure, such as physical space and energy capacity restrictions. It is not impossible, though; it might only be more challenging to do.

Furthermore, we also have another scenario in which our infrastructure, either on the cloud or on-premises, already has those computing resources. In this case, we just need to start using them to accelerate the training process.

So, if we have money to buy or contract these resources, or if they are already available to us in our environment, the problem is solved, right? Not necessarily. Unfortunately, there is no guarantee that using additional resources in the training process will automatically improve performance. As we will discuss in this book, the performance bottleneck is not always overcome by adding more computing resources without rethinking the whole process, adjusting the code, and so on.

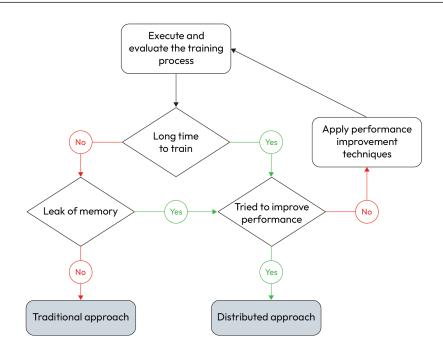

This last assertion gives us a valuable lesson: we must see these two approaches as a cycle, not as two isolated options. This means we must go back and forth on both methods as often as necessary to reach the desired improvement, as shown in *Figure 2.2*:

Figure 2.2 – Continuous improvement cycle

Let's see more details about both approaches in the following sections.

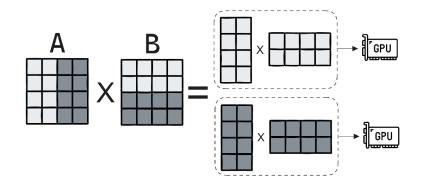

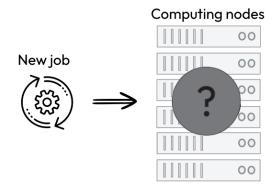

### Modifying the software stack

The software stack used to train a model can vary depending on the environment we use to execute this process. For the sake of simplicity, we will consider in this book a software stack seen from the point of view of data scientists, i.e., as users of a computing service or environment.

In general, we can say the software stack looks like the layers shown in Figure 2.3:

Figure 2.3 – Software stack used to train a model

From the top to the bottom, we have the following layers:

- 1. **Application**: The model-building program occupies this layer. This program can be written in any programming language capable of building neural networks, such as R and Julia, but Python is the language primarily used for this purpose.

- 2. Environment: The machine learning framework used to build the application, libraries, and tools used to support this framework lie in this layer. Some examples of machine learning frameworks are PyTorch, TensorFlow, Keras, and MxNet. Concerning the set of libraries, we can cite Nvidia Collective Communication Library (NCCL), for efficient communication among GPUs, and jemalloc, for optimized memory allocation.

- 3. **Execution**: This layer is responsible for supporting the execution of the environment and application layers. Therefore, a container solution or bare metal operating system belongs to this layer. Although the components of the upper layers can be executed directly on the operating system, nowadays, it is common to use a container to wrap up the entire application and its environment. Although Docker is the most famous container solution, it is preferable to adopt a more suitable option to run machine learning workloads such as **Apptainer** and **Enroot**.

At the bottom of the software stack, there is a box representing all the hardware resources needed to execute the upper software layers.

To obtain a practical understanding of this software stack representation, let's see a couple of examples, as illustrated in *Figure 2.4*:

Figure 2.4 – Examples of software stacks

All scenarios described in *Figure 2.4* use an application written in Python. As stated before, the application can be a program coded in C++ or a script written in R. It does not matter. The important note to keep in mind is that the application layer represents the location of our code. In examples **A**, **B**, and **D**, we have scenarios using PyTorch as the machine learning framework. Cases **A** and **B** have the support of additional libraries, namely **OpenMP** and **Intel One API**. This means PyTorch is relying on these libraries to empower tasks and operations.

Finally, the execution layer of scenarios **B** and **C** uses a container solution to execute the upper layers, whereas the upper layers of examples **A** and **D** run directly on the operating system. Furthermore, notice that the hardware resources in scenarios **B** and **C** are endowed with GPU accelerators, whereas the others have only a CPU.

#### Important note

Remark that we are abstracting the type of infrastructure used to run the software stack since it is irrelevant to our discussion at this moment. Therefore, you can consider the software stack hosted in a cloud or on-premises infrastructure.

Except for the case where we are using an environment provided by our own resources, we probably will not have the administrative rights to modify or add configurations in the execution layer. In most cases, we use the computing environments provisioned by our companies. Thus, we do not possess the privilege to alter anything in the container or operating system layers. Usually, we address these modifications to the IT infrastructure team.

For this reason, we will focus on the application and environment layers, where we have the power to change and perform additional configurations.

The second part of this book focuses on teaching you how to change the software stack in such a way that we can accelerate the training process with the available resources.

#### Important note

There are exciting configurations we can make in the execution layer to improve performance. However, they are out of the scope of this book. As data scientists are the primary audience of this material, we focus on the layers that these professionals have the necessary access to modify and customize by themselves.

Modifying the software stack to accelerate the training process has a limit. We get stuck on performance improvement, no matter how deep and advanced the techniques we use are. When we reach that limit, the one way to speed up the training phase is by using additional computing resources, as explained in the next section.

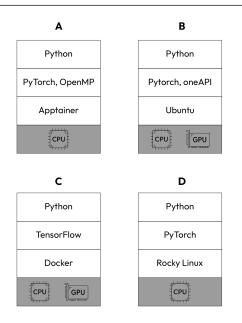

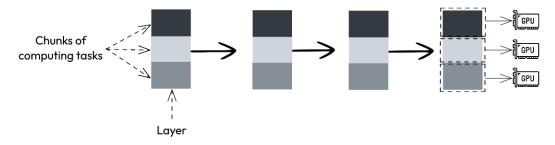

#### Increasing computing resources

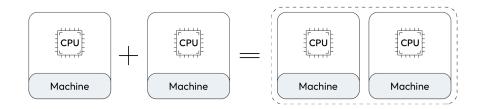

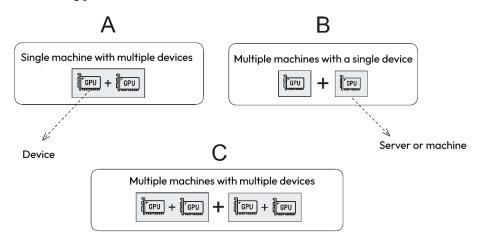

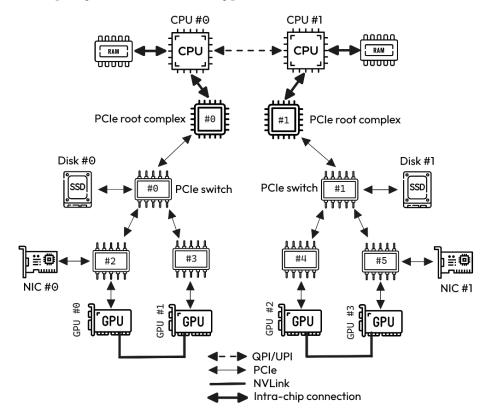

There are two approaches to increasing computing resources in an existing environment: vertical and horizontal scaling. In vertical scaling, we augment the computing resources of a single machine, whereas, in horizontal scaling, we add more machines to the pool of equipment used to train the model.

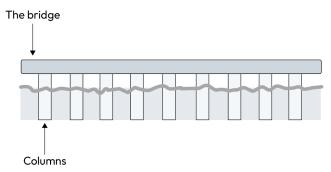

In practical terms, **vertical scaling** allows for equipping the machine with an accelerator device to increase main memory, add more processor cores, and so on, as exemplified in *Figure 2.5*. After doing this scaling, we obtain an empowered machine with higher resources:

Figure 2.5 – Example of vertical scaling

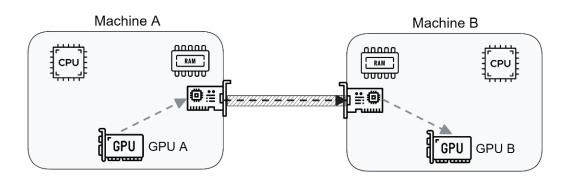

Horizontal scaling is related to the increase in the number of machines used by our application. If we originally used one machine to execute the training process, we can apply horizontal scaling and use two machines to work together to train the model, as shown in the example of *Figure 2.6*:

Figure 2.6 – Example of horizontal scaling

Regardless of the type of scaling, we need to know how to harness these additional resources to improve performance. Depending on the kind of resources added to our setup, we need to adjust the code in many different parts. In other situations, the machine learning framework can automatically deal with the increase in resources without requiring any additional modification.

As we learned in this section, the first step to accelerate the training process relies on modifying the application layer. Follow me to the next section to know how to do it.

## Modifying the application layer

The application layer is the starting point of the performance improvement journey. As we have complete control of the application code, we can change it without depending on anyone else. Thus, there is no better way to start the performance optimization process than working independently.

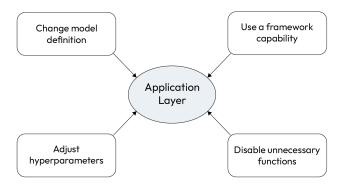

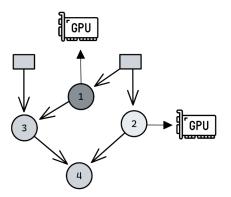

## What can we change in the application layer?

You may wonder how we can modify the code to improve performance. Well, we can reduce model complexity, increase the batch size to optimize memory usage, compile the model to fuse operations and disable profiling functions to eliminate extra overhead in the training process.

Regardless of the changes applied to the application layer, we cannot sacrifice model accuracy in favor of performance improvement since this does not make sense. As the primary goal of a neural network is to solve problems, it would be meaningless to accelerate the building process of a useless model. Then, we must pay attention to model quality when modifying the code to reduce the training phase time.

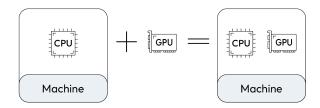

In *Figure 2.7*, we can see the sort of changes we can make in the application layer to speed up the training phase:

Figure 2.7 – Changes in the application layer to accelerate the training process

Let's look at each of the changes:

- **Change model definition**: Modify the neural network architecture to reduce the number of layers, weights, and operations executed on each layer

- Adjust hyperparameters: Change hyperparameters such as batch size, the number of epochs, and the optimizer

- Use a framework capability: Take advantage of a framework capability such as kernel fusion, automatic mixed precision, and model compiling

- **Disable unnecessary functions**: Get rid of undue burdens such as computing the gradient on the validation phase

#### Important note

Some framework capabilities rely on making changes in the environment layer, such as installing an additional tool or library or even upgrading the framework version.

Naturally, these categories do not cover all possibilities for performance improvement in the application layer; their purpose is to give you a clear mental model of what we can effectively do to the code to accelerate the training phase.

### Getting hands-on

Let's see a practical example of performance improvement by changing only the application code. Our guinea pig is the CNN model introduced in the previous chapter, which was used to classify the images of the Fashion-MNIST dataset.

#### Important note

Details about the computing environment used in this experiment are irrelevant at this time. What truly matters is the speedup achieved with these modifications, considering the same environment and conditions.

This model has two convolutional layers and two fully connected layers, resulting in **1,630,090** weights. With the number of epochs equal to 10 and the batch size equal to 64, the training phase took 148 seconds to complete. The trained model achieved 83.99% accuracy when tested against 10,000 images from the test dataset, as you can see here:

```

Epoch [1/10], Loss: 0.9136

Epoch [2/10], Loss: 0.6925

Epoch [3/10], Loss: 0.7313

Epoch [4/10], Loss: 0.6681

Epoch [5/10], Loss: 0.3191

Epoch [6/10], Loss: 0.5790

Epoch [6/10], Loss: 0.4824

Epoch [8/10], Loss: 0.4824

Epoch [8/10], Loss: 0.6229

Epoch [9/10], Loss: 0.7279

Epoch [10/10], Loss: 0.3292

Training time: 148 seconds

Accuracy of the network on the 10000 test images: 83.99 %

```

#### Important note

The complete code shown in this section is available at https://github.com/ PacktPublishing/Accelerate-Model-Training-with-PyTorch-2.X/ blob/main/code/chapter02/baseline.ipynb.

By making only one simple modification to the code, we can reduce the training time of this model by 15% while keeping the same accuracy achieved with the baseline code. The improved code took 125 seconds to complete, and the trained model reached an accuracy equal to 83.76%:

```

Epoch [1/10], Loss: 1.0960

Epoch [2/10], Loss: 0.6656

Epoch [3/10], Loss: 0.6444

Epoch [4/10], Loss: 0.6463

Epoch [5/10], Loss: 0.4772

Epoch [6/10], Loss: 0.4700

Epoch [8/10], Loss: 0.4800

Epoch [9/10], Loss: 0.4885

```

```

Epoch [10/10], Loss: 0.4708

Training time: 125 seconds

Accuracy of the network on the 10000 test images: 83.76 %

```

#### Important note

```

The complete code shown in this section is available at https://github.com/

PacktPublishing/Accelerate-Model-Training-with-PyTorch-2.X/

blob/main/code/chapter02/application_layer-bias.ipynb.

```

We improved performance by disabling the bias parameter on the two convolutional and two fully connected layers. The following piece of code shows the use of the bias parameter to disable the bias weight on the function's Conv2d and Linear layers:

```

def __init__(self, num_classes=10):

super(CNN, self).__init__()

self.layer1 = nn.Sequential(

nn.Conv2d

(1, 32, kernel_size=3, stride=1,padding=1, bias=False),

nn.ReLU(),

nn.MaxPool2d(kernel_size = 2, stride = 2))

self.layer2 = nn.Sequential(

nn.Conv2d

(32, 64, kernel_size=3,stride=1,padding=1, bias=False),

nn.ReLU(),

nn.ReLU(),

nn.MaxPool2d(kernel_size = 2, stride = 2))

self.fc1 = nn.Linear(64*7*7, 512, bias=False)

self.fc2 = nn.Linear(512, num_classes, bias=False)

```

This modification reduced the number of weights from 1,630,090 to 1,629,472, representing a decrease of only 0.04% in the total number of neural network weights. As we can see, this change in the number of weights did not affect the model's accuracy since it achieved practically the same efficiency as before. Therefore, we trained the model 15% faster with almost no additional effort.

#### What if we change the batch size?

If we double the batch size from 64 to 128, we achieve an even better performance gain than disabling the bias:

Epoch [1/10], Loss: 1.1859 Epoch [2/10], Loss: 0.7575 Epoch [3/10], Loss: 0.6956

```

Epoch [4/10], Loss: 0.6296

Epoch [5/10], Loss: 0.6997

Epoch [6/10], Loss: 0.5369

Epoch [7/10], Loss: 0.5247

Epoch [8/10], Loss: 0.5866

Epoch [9/10], Loss: 0.4931

Epoch [10/10], Loss: 0.4058

Training time: 96 seconds

Accuracy of the network on the 10000 test images: 82.14 %

```

#### Important note

The complete code shown in this section is available at https://github.com/ PacktPublishing/Accelerate-Model-Training-with-PyTorch-2.X/ blob/main/code/chapter02/application\_layer-batchsize.ipynb.

We trained the model 54% faster by doubling the batch size. As we learned in *Chapter 1*, *Deconstructing the Training Process*, the batch size dictates the number of steps in the training phase. Because we increased the batch size from 64 to 128, we obtained a fewer number of steps per epoch, i.e., the number of steps passed from 938 to 469. As a consequence, the learning algorithm executes half of the phases needed to complete an epoch.

However, such modification came with a price: the accuracy was reduced from 83.99% to 82.14%. This happens because the learning algorithm executes the optimization phase per each training step. Since the number of steps reduced and the number of epochs remained the same, the learning algorithm executed a fewer number of optimization phases, which consequently decreases its opportunity to reduce the training cost.

Just out of curiosity, let's see what happens when changing the batch size to 256:

```

Epoch [1/10], Loss: 1.5919

Epoch [2/10], Loss: 0.9232

Epoch [3/10], Loss: 0.8151

Epoch [4/10], Loss: 0.6488

Epoch [5/10], Loss: 0.7208

Epoch [6/10], Loss: 0.5085

Epoch [7/10], Loss: 0.5984

Epoch [8/10], Loss: 0.5603

Epoch [9/10], Loss: 0.6575

Epoch [10/10], Loss: 0.4694

Training time: 76 seconds

Accuracy of the network on the 10000 test images: 80.01 %

```

The training time was reduced even more, though not as significantly as when we changed from 64 to 128. On the other hand, the model efficiency fell to 80%. We can also observe an increase in the loss per epoch when compared to the previous test.

In short, we have to find the balance between training speedup and model efficiency when adjusting the batch size. The ideal batch size value depends on the model architecture, dataset characteristics, and the hardware resource used to train the model. Thus, the best way to define it is by doing some experiments before starting the training process for real.

These simple examples showed is possible to accelerate the training process by making direct modifications to the code. In the next section, we will see what kind of changes we can make in the environment layer to speed up model training.

## Modifying the environment layer

The environment layer comprises the machine learning framework and all the software needed to support its execution, such as libraries, compilers, and auxiliary tools.

## What can we change in the environment layer?

As we discussed before, we may not have the necessary permission to change anything in the environment layer. This restriction depends on the type of environment we use to train the model. In third-party environments, such as notebook's online services, we do not have the flexibility to make advanced configurations, such as downloading, compiling, and installing a specialized library. We can upgrade a package or install a new library, but nothing beyond that.

To overcome this restriction, we commonly use **containers**. Containers allow us to configure anything we need to run our application without requiring the support or permission of everyone else. Obviously, we are talking about the environment layer and not about the execution layer. As we discussed previously, making changes to the execution layer requires administrative privileges, which would be out of our hands in most environments we usually use.

#### Important note

The complete code shown in this section is available at https://github.com/ PacktPublishing/Accelerate-Model-Training-with-PyTorch-2.X/ blob/main/code/chapter02/environment\_layer.ipynb.

In the case of the environment layer, we can modify these sorts of things:

• Install and use a specialized library: The machine learning framework comes with everything we need to train a model. However, we can speed up the training process by using libraries specialized in tasks such as memory allocation, math operations, and collective communication.

- **Control libraries' behavior through environment variables**: The default behavior of libraries cannot be the best one for a given scenario or specific setup. In that case, we can change it directly through environment variables from the application code.

- Upgrade framework and libraries to new versions: This may sound silly, but upgrading the machine learning framework and libraries to new versions can raise the performance of the training process much more than we think.

We are going to learn many of these things throughout this book. For now, let's jump to the next section to see performance improvement in practice.

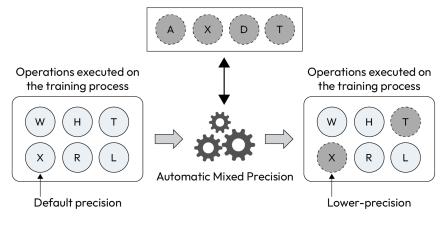

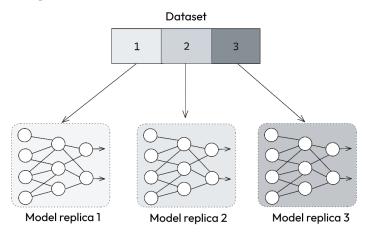

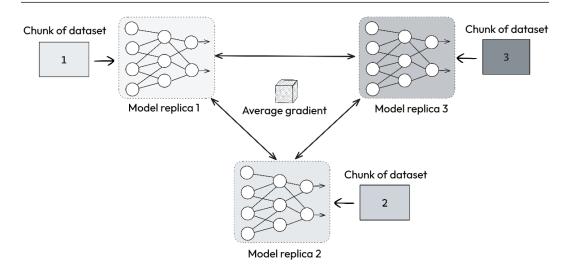

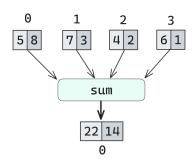

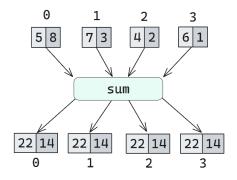

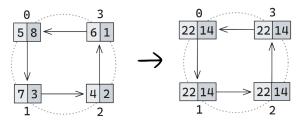

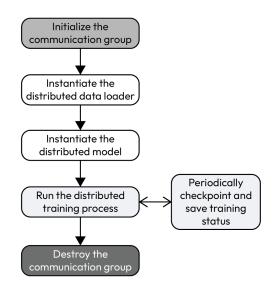

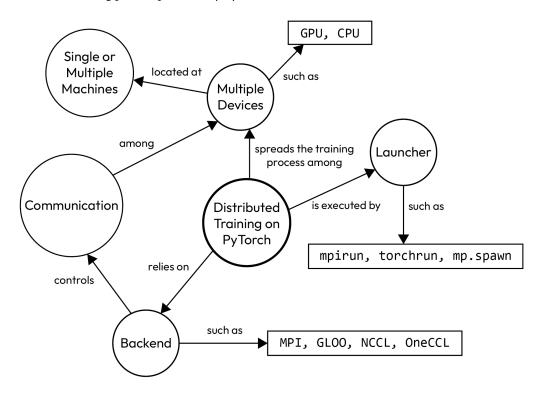

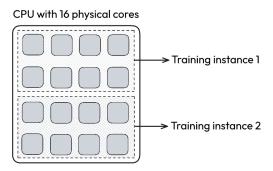

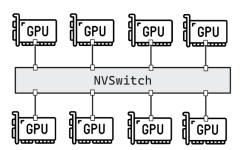

#### Getting hands-on